[Vitis Unified Ide]入门

实验前请确保开发板的BOOT处于JTAG模式

实验目的

本实验将通过Vitis Unified Ide进行点灯。同时将展示三种GPIO控制方法:MIO,EMIO,AXI_GPIO

前置知识

ZYNQ SoC 的 PS(Processing System)和 PL(Programmable Logic)

PS即处理器系统(ARM),PL即可编程逻辑(FPGA)

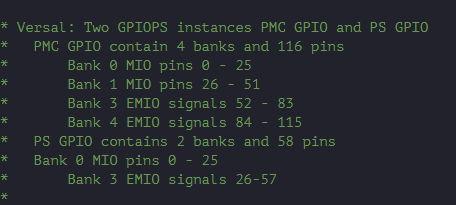

GPIO(General Purpose I/O),通用输入输出,是 ZYNQ 的外设之一。GPIO包括 MIO 与 EMIO,是 ZYNQ 上最常用的硬件资源。MIO 分配在 GPIO 的 Bank0 和Bank1,属于 ZYNQ 的 PS 部分, 而 EMIO 也是 PS 上 GPIO 的一部分,但连接到了PL, 分配在 GPIO 的 Bank2 和 Bank3。MIO 在芯片外部有 54 个引脚,这些引脚可以用于 GPIO、SPI、UART、USB 等功能上,每个引脚都同时具有多种功能。因为MIO 是 PS 部分的引脚且其操作对于 PL 端不可见,所以对 MIO 的操作可以视为纯 PS 端的操作。EMIO 有 64 个引脚, EMIO 与 MIO 的不同在于,EMIO 连接到了PL,再从 PL 输出信号,而 MIO 直接从 PS 端输出。

**MIO: ** PS –> GPIO(PS)

**EMIO: **PS –> PL –> GPIO(PL)

**AXI_GPIO: **PS -(AXI)-> PL –> GPIO(PL)

上面是三种控制方法的简单流图

实验步骤

新建项目

先建立Vivado项目,用于后续生成硬件描述文件(.xsa)

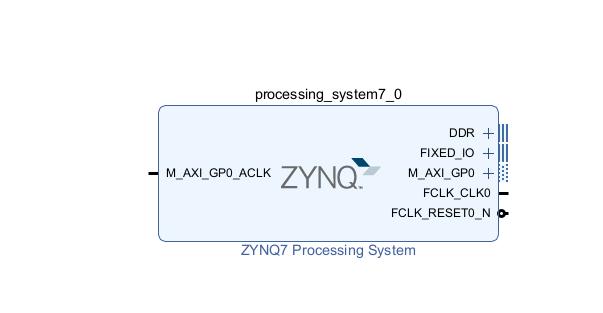

Create Block Design 并添加ZYNQ ip核

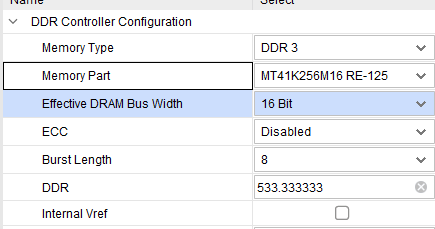

接下来需要配置DDR(双击ZYNQ ip打开配置界面)。对于小梅哥的BX71配置如下。野火的将DRAM位宽改为332bit即可。

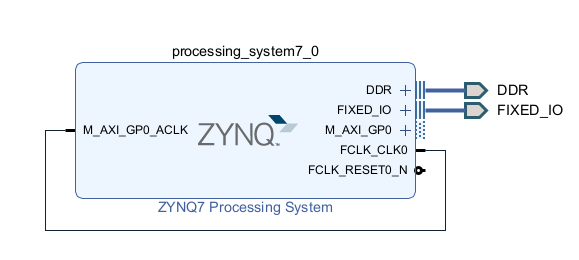

点击OK关闭设置弹窗后点击Run Block Automation进行DDR的自动连接。在未进行AXI_GPIO实验时,我们需要先将FCLK_CLK0和M_AXI_GP0_ACLK连接起来

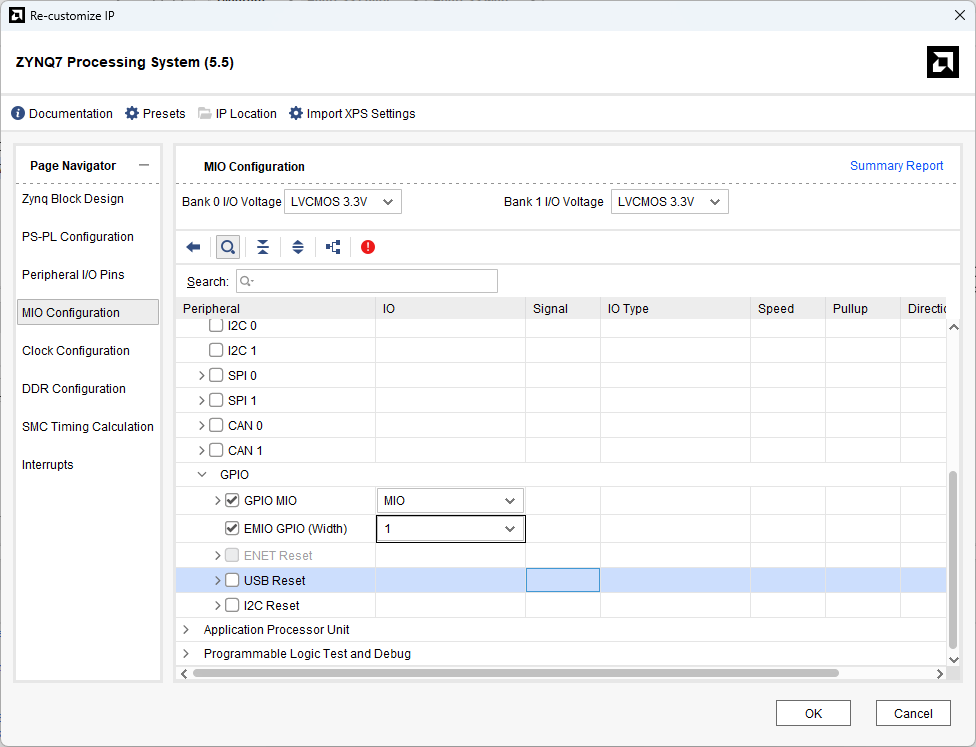

接下来重新双击ZYNQ ip进行GPIO配置

对于小梅哥开发板上的LED_IO

| Signial Name. | Pin NO. |

|---|---|

| PS_LED0 | PS_MIO0 |

| FPGA_LED0 | T10 |

其它开发板自行查询手册

配置

配置如下

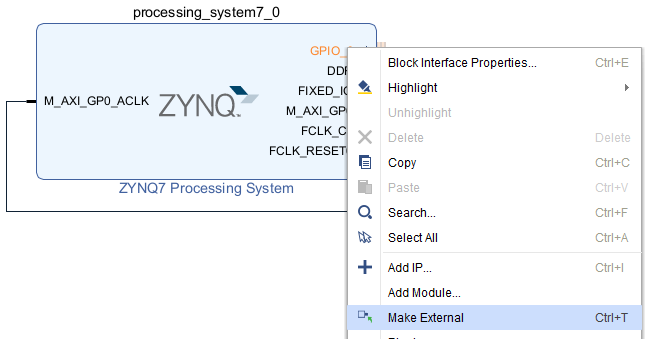

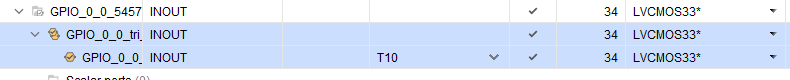

右键GPIO_0引出端口

绑定引脚

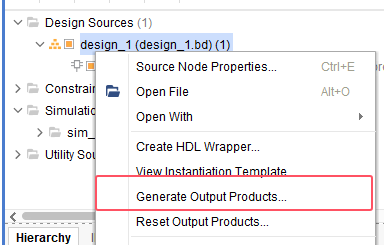

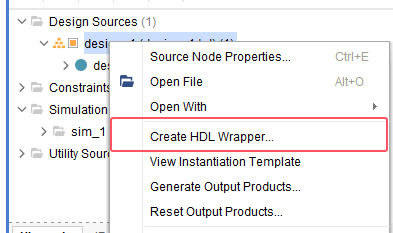

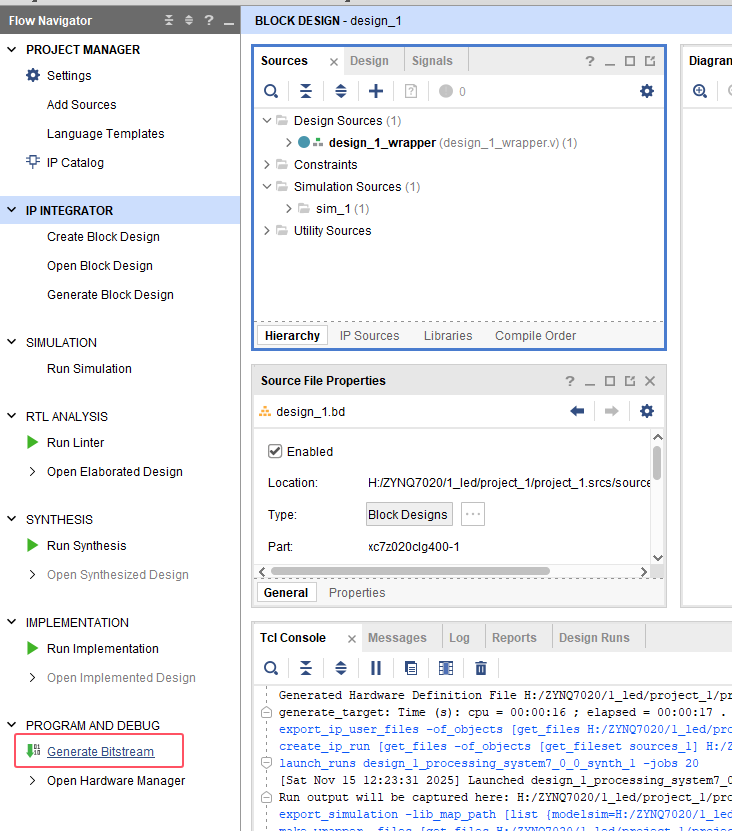

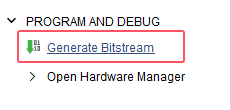

生成bit流

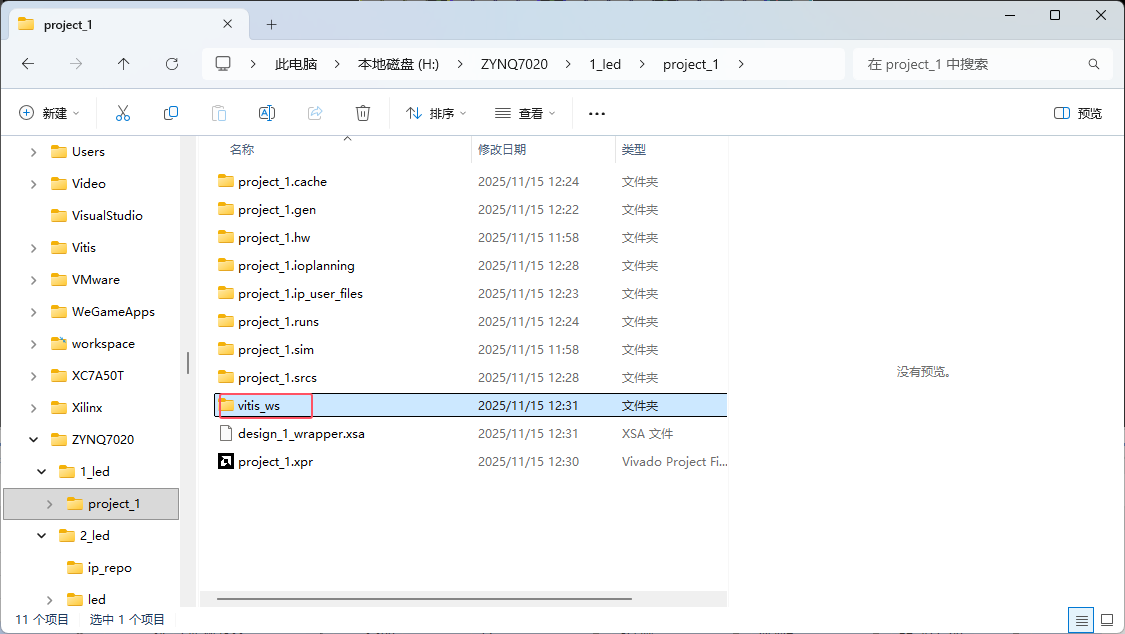

接下来我们在项目文件夹内新建一个文件夹用来存放vitis工程

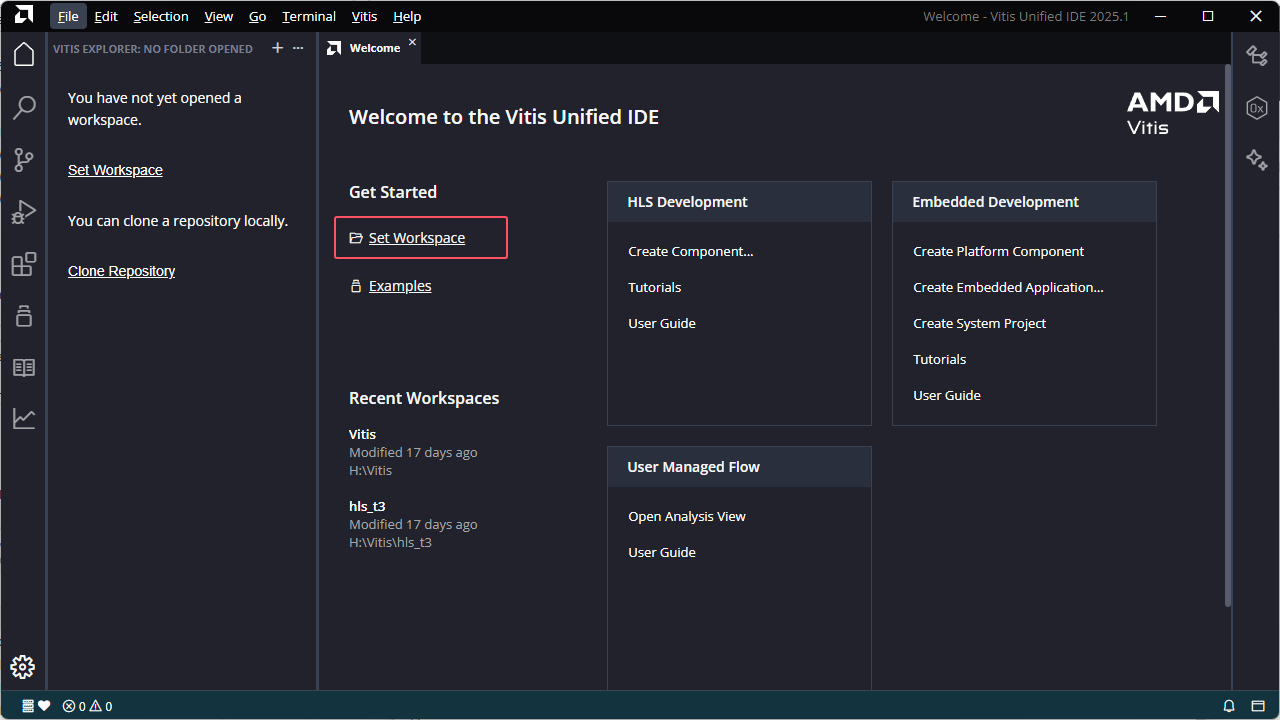

打开vitis,选择Set Workspace,选择刚刚新建的文件夹

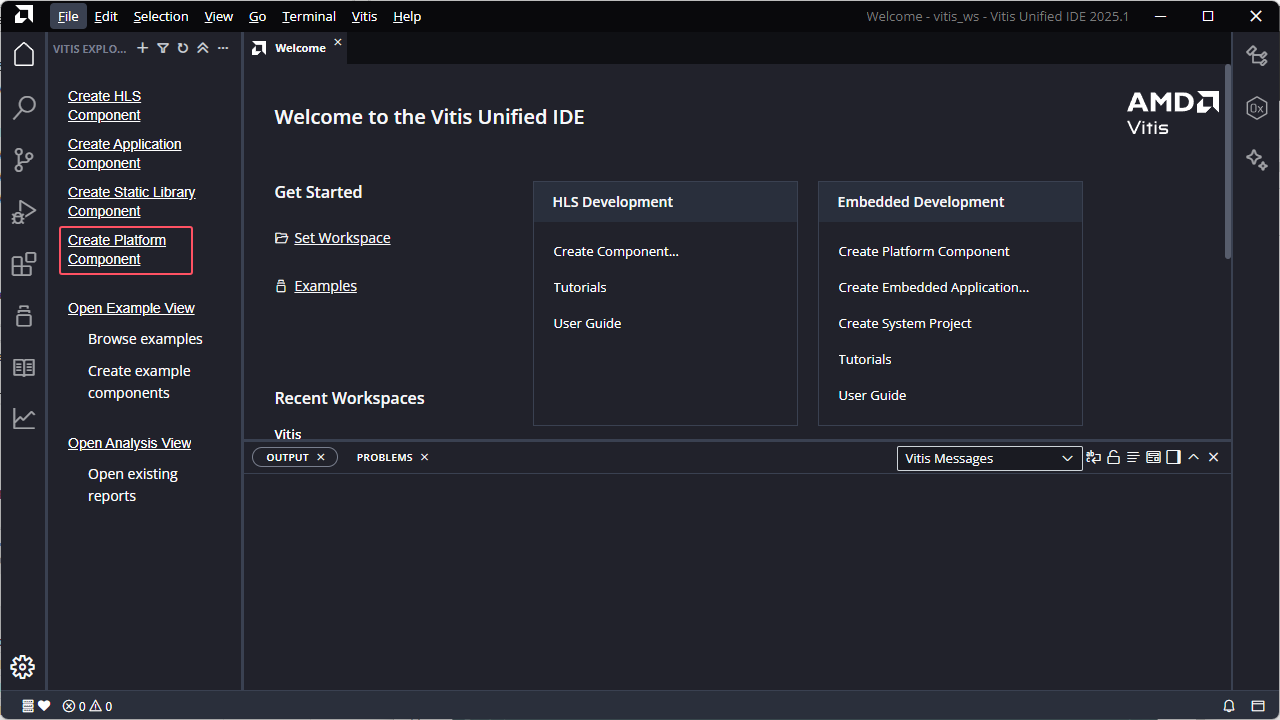

接下来我们新建一个Platform Component

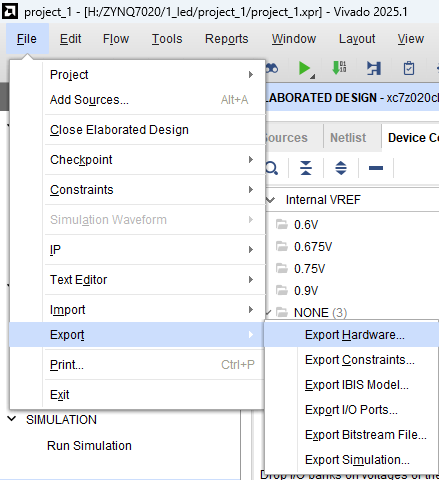

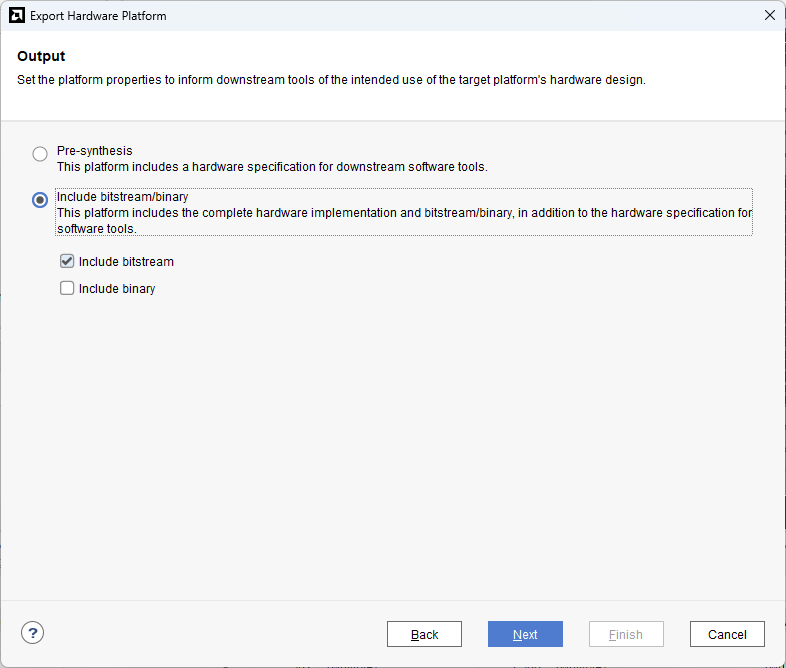

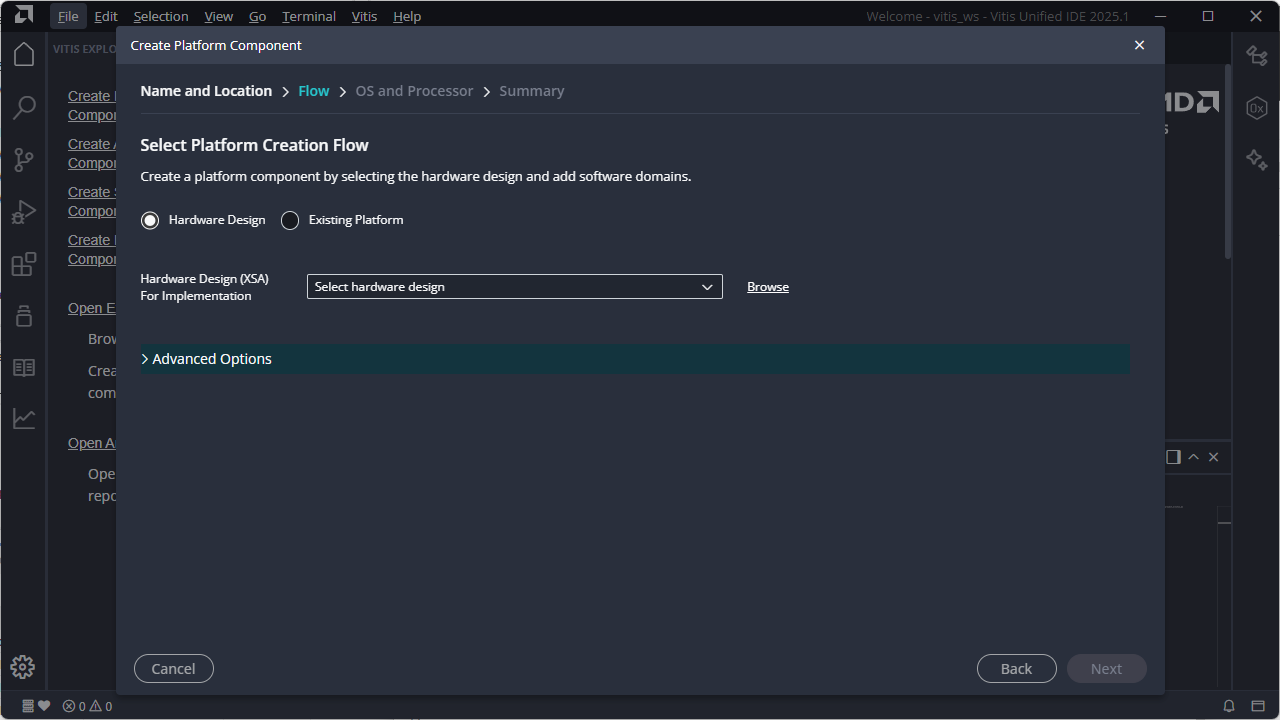

此处选择在vivado项目根目录下的.xsa文件

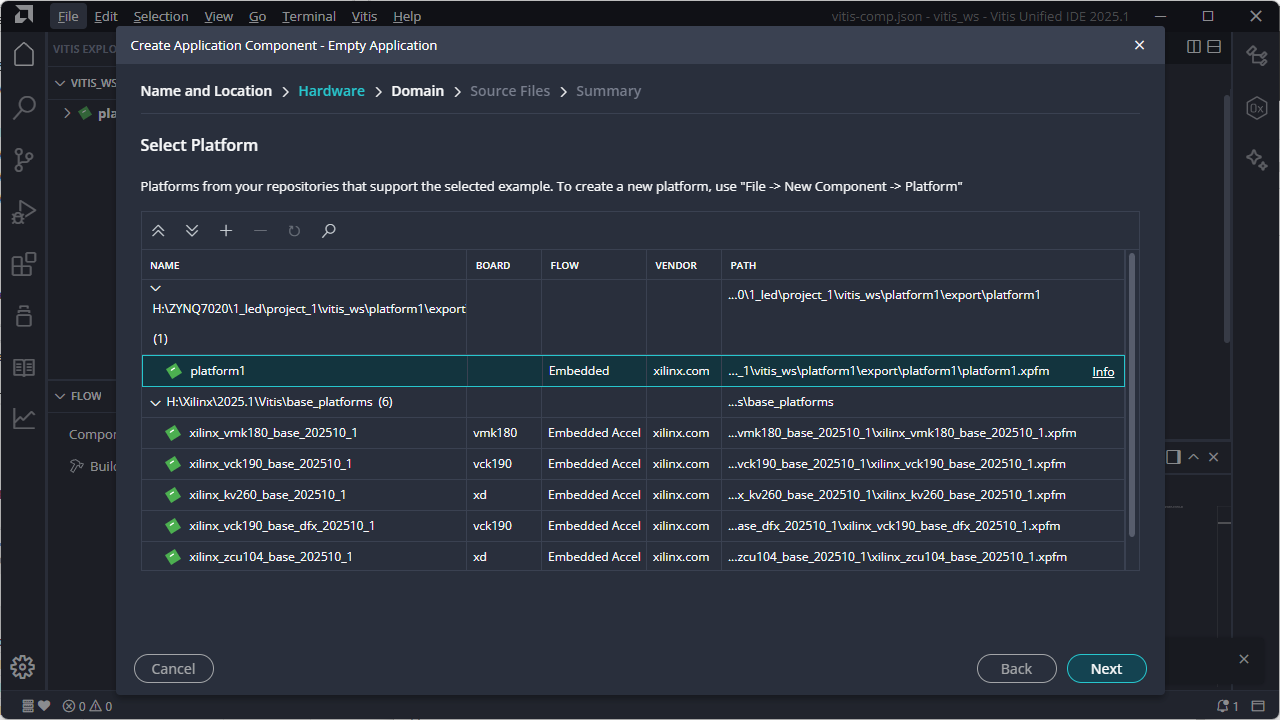

再建立Application Component

此处选择刚刚新建的platform

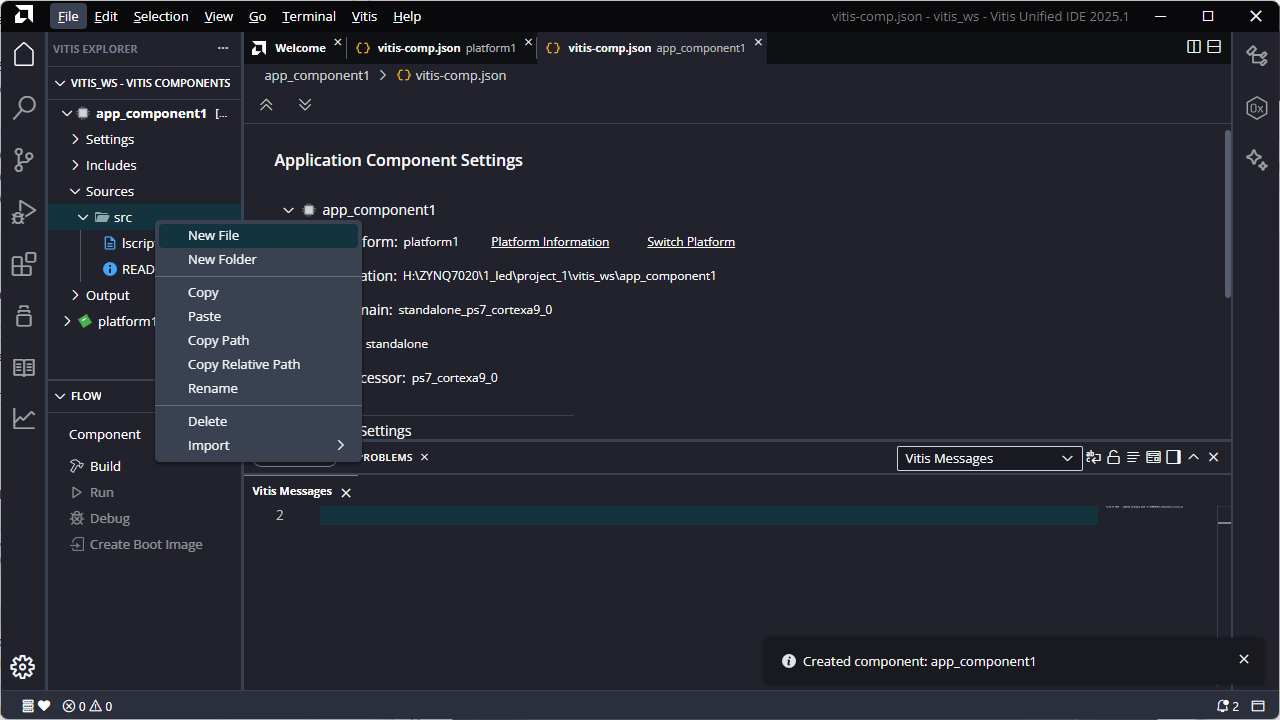

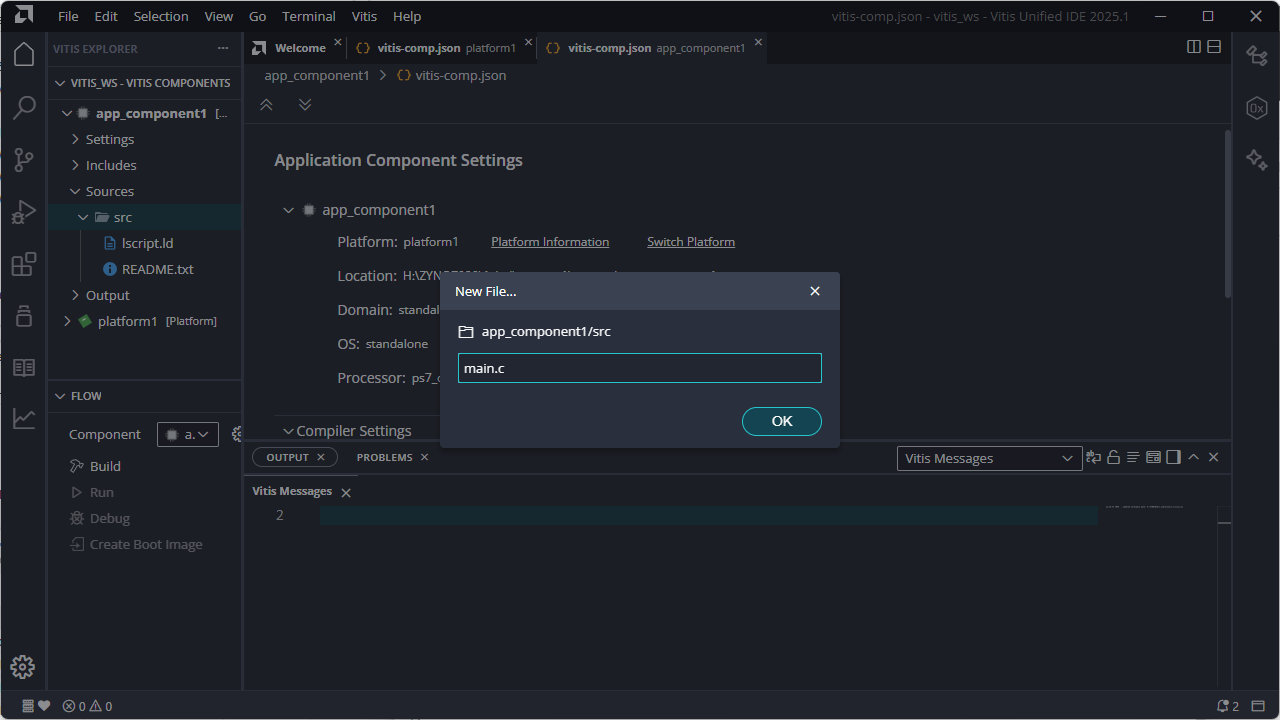

右键src新建C语言代码文件

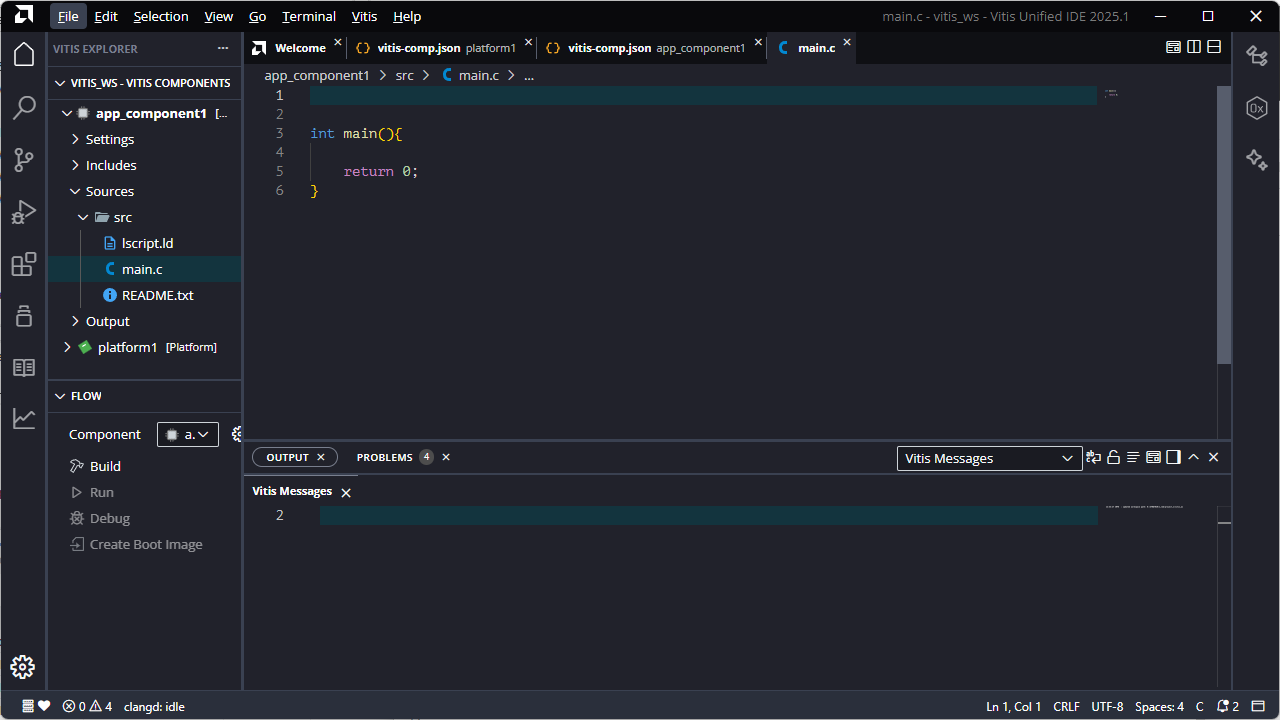

导入#include "xparameters.h" xgpiops.h

ctrl+左键进入xgpiops.h

圈出部分就是ZYNQ7020对应的MIO/EMIO

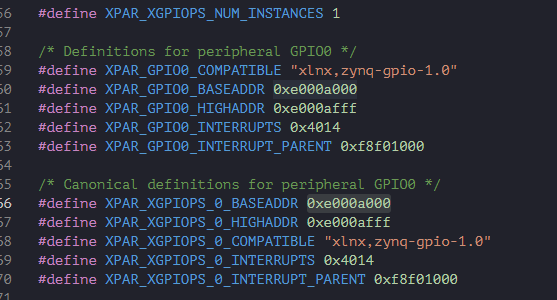

"xparameters.h"中GPIO的BASEADDR

代码部分

代码如下。可以观察到两个LED循环闪烁

1 |

|

![[RK3588]初识随笔](https://www.rock-chips.com/uploads/allimg/220926/1-2209261629510.png)

![[Vitis Unified Ide]入门](https://www.amd.com/content/dam/amd/en/images/covers/2772134-vitis-software-box.png)